Exploring SystemVerilog Packages: A Comprehensive Guide

Exploring SystemVerilog Packages: A Comprehensive Guide

In the world of SystemVerilog, packages play a crucial role in organizing and managing your code. They provide a way to encapsulate related declarations, data types, and functions for easy reuse. This comprehensive guide will take you through the ins and outs of SystemVerilog packages and how you can leverage them effectively in your designs.

Understanding SystemVerilog Packages

A SystemVerilog package is a collection of data types, constants, functions, and tasks that can be easily reused across multiple files. By encapsulating related elements within a package, you can improve code organization, promote reusability, and enhance readability.

When you import a package into your SystemVerilog design, you gain access to all the elements defined within that package. This can significantly reduce the amount of code you need to write and maintain, leading to more efficient development cycles.

Creating and Importing Packages

To create a SystemVerilog package, you simply define the elements you want to include within the package scope. Here’s an example of a basic package that defines some common data types:

package MyPackage;

typedef logic [7:0] byte_t;

typedef enum logic [2:0] {RED, GREEN, BLUE} color_t;

endpackage

Once you have defined your package, you can import it into your SystemVerilog files using the `import` directive:

import MyPackage::*;

By importing the package with `*`, you bring in all the elements from the package into your current scope, making them accessible for use in your code.

Benefits of Using Packages

Using SystemVerilog packages offers several key benefits:

- Modularity: Packages allow you to modularize your code and group related elements together.

- Reusability: By encapsulating code within a package, you can easily reuse it across multiple files.

- Readability: Packages help improve code readability by structuring elements in a coherent manner.

Additionally, packages provide a way to manage namespaces in SystemVerilog, preventing naming conflicts and making it easier to maintain large projects.

In Conclusion

Exploring SystemVerilog packages can open up new possibilities for code organization and reuse in your designs. By taking advantage of packages, you can streamline your development process and create more maintainable and efficient code.

-

01

Packaging Machinery: Beyond Sealing, Driving an Efficient, Smart, and Sustainable Future

21-01-2026 -

02

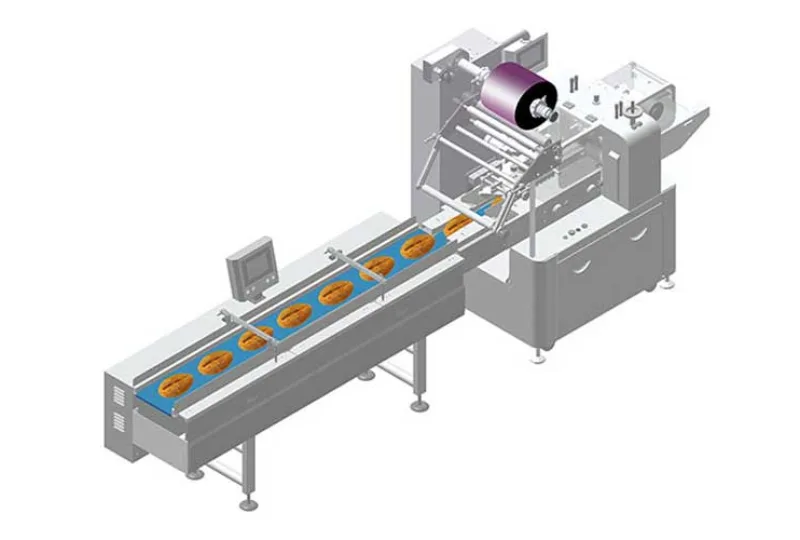

Automatic Tray Loading and Packaging Equipment: Boost Efficiency to 160 Bags/Minute

21-11-2025 -

03

Automatic Soap Packaging Machine: Boost Productivity with 99% Qualification Rate

21-11-2025 -

04

A Deep Dive into Automatic Toast Processing and Packaging System

18-11-2025 -

05

The Future of Bakery Production: Automated Toast Processing and Packaging System

18-11-2025 -

06

Reliable Food Packaging Solutions with China Bread, Candy, and Biscuit Machines

11-10-2025 -

07

High-Performance Automated Food Packaging Equipment for Modern Production

11-10-2025 -

08

Reliable Pillow Packing Machines for Efficient Packaging Operations

11-10-2025 -

09

Advanced Fully Automatic Packaging Solutions for Efficient Production

11-10-2025 -

10

Efficient Automatic Food Packaging Solutions for Modern Production

11-10-2025