Mastering SystemVerilog Packages for Efficient Coding

The Power of SystemVerilog Packages in Efficient RTL Coding

In the realm of hardware description languages, mastering SystemVerilog is a transformative journey. Among its many features, SystemVerilog packages stand out as a versatile tool for encapsulating design elements and fostering reusability. In this post, we delve deep into the realm of SystemVerilog packages, exploring their significance and how they elevate RTL coding efficiency.

SystemVerilog packages serve as containers for functions, tasks, and data types, offering modular structuring capabilities. By encapsulating related elements within packages, designers can isolate functionalities, enhancing organization and facilitating code readability. This approach reduces the complexities associated with maintaining large RTL designs, promoting modularity and ease of debugging.

Benefits of Leveraging SystemVerilog Packages

One of the primary advantages of utilizing SystemVerilog packages is the facilitation of hierarchical design structures. By hierarchically organizing design components into packages, developers can create logical groupings that mirror the design’s architecture. This hierarchical structuring simplifies design navigation and promotes a systematic approach to RTL development.

Moreover, SystemVerilog packages enable designers to define and share reusable components across multiple modules. By encapsulating commonly used functions and data types within packages, developers can leverage these components seamlessly throughout the design, fostering reusability and promoting design consistency.

Best Practices for SystemVerilog Packages

When incorporating SystemVerilog packages into RTL designs, adherence to best practices is essential to maximize their effectiveness. Designers should adopt a standardized naming convention for packages and their contents to enhance clarity and maintainability.

Additionally, carefully structuring packages to encapsulate related functionalities improves code modularity and facilitates future design modifications. By following a consistent package organization strategy, developers can enhance code readability and streamline design maintenance.

Exploring Advanced Applications of SystemVerilog Packages

As designers delve deeper into SystemVerilog, they uncover advanced applications of packages that extend beyond basic modularization. Leveraging parameterized classes within packages empowers developers to create flexible and customizable RTL components, enhancing design scalability and versatility.

Furthermore, combining SystemVerilog packages with interfaces unlocks a new realm of possibilities for designing complex and interconnected systems. By encapsulating interface definitions and implementations within packages, developers can streamline system-level integration and promote design scalability.

Embracing the Future of RTL Design with SystemVerilog Packages

SystemVerilog packages represent a fundamental building block in the evolution of RTL design methodologies. By harnessing the power of encapsulation, reusability, and hierarchy, designers can elevate their coding efficiency and unlock new horizons in hardware design.

As the semiconductor industry continues to evolve, mastering SystemVerilog packages will be imperative for staying ahead of the curve. Embracing the versatility and power of packages equips designers with the tools needed to tackle complex design challenges and innovate in the rapidly changing landscape of hardware design.

-

01

01Packaging Machinery: Beyond Sealing, Driving an Efficient, Smart, and Sustainable Future

21-01-2026 -

02

02Automatic Tray Loading and Packaging Equipment: Boost Efficiency to 160 Bags/Minute

21-11-2025 -

03

03Automatic Soap Packaging Machine: Boost Productivity with 99% Qualification Rate

21-11-2025 -

04

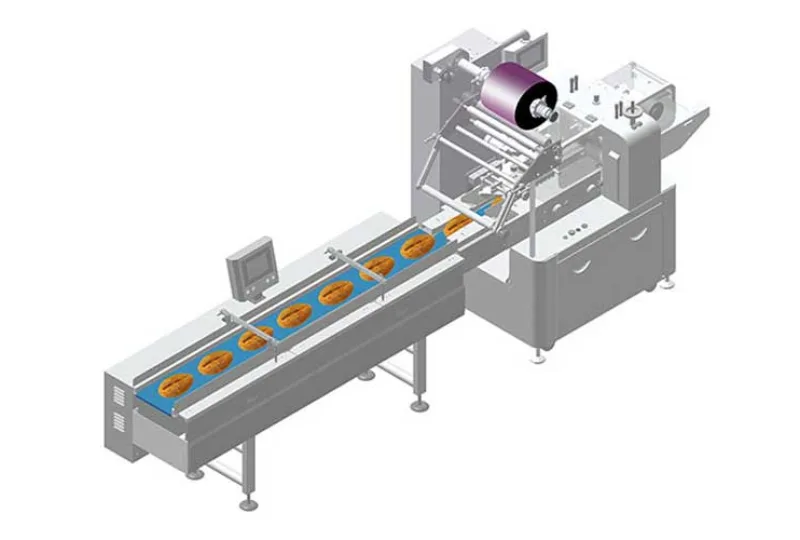

04A Deep Dive into Automatic Toast Processing and Packaging System

18-11-2025 -

05

05The Future of Bakery Production: Automated Toast Processing and Packaging System

18-11-2025 -

06

06Reliable Food Packaging Solutions with China Bread, Candy, and Biscuit Machines

11-10-2025 -

07

07High-Performance Automated Food Packaging Equipment for Modern Production

11-10-2025 -

08

08Reliable Pillow Packing Machines for Efficient Packaging Operations

11-10-2025 -

09

09Advanced Fully Automatic Packaging Solutions for Efficient Production

11-10-2025 -

10

10Efficient Automatic Food Packaging Solutions for Modern Production

11-10-2025